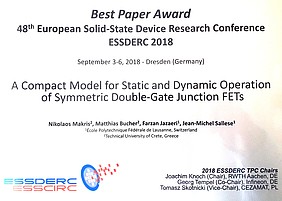

Nikos Makris, Ph.D. student, and Associate Professor Matthias Bucher of the Electronics Laboratory (School of ECE/Technical University of Crete), were selected for the European Solid-State Device Research Conference (ESSDERC) 'Best Paper Award' for the paper:

Nikolaos Makris, Matthias Bucher, Farzan Jazaeri, Jean-Michel Sallese. A Compact Model for Static and Dynamic Operation of Symmetric Double-Gate Junction FETs. Proceedings of the 48th European Solid-State Device Research Conference (ESSDERC), 2018.

The award was announced at the ESSDERC conference, Cracow, Poland, September 23-26, 2019. ESSDERC is the premier conference in solid-state devices in Europe. ESSDERC announces one 'Best Paper Award' and one 'Young Scientist Best Paper Award', annually.

The paper describes a novel, analytical and charge-based compact model, which describes in an elegant way the static and dynamic behavior of the double gate Junction Field Effect Transistor (JFET). The model aims at the efficient and accurate design and simulation of JFET integrated circuits. JFETs are used in low-noise electronics, with applications in bioelectronics, astronomy etc., but also in applications under harsh conditions such as radiation, high/low temperatures, and power electronics for energy saving.

The paper was presented in September, 3-6 2018, in Dresden, Germany and is the result of a cooperation of the group of Prof. M. Bucher with the group at EPFL, Lausanne, Switzerland.

Abstract of the paper:

The present work describes a novel charge-based compact model of the symmetric double-gate junction field effect transistor (DG JFET) for circuit simulation. The model is physics-based and addresses static and capacitive behavior of the JFET. The model covers all regions of device operation of the depletion mode JFET, relies only on physical and electrical parameters of the device, and includes short-channel effects. The model is validated with respect to TCAD simulation as well as with respect to measurements from JFETs. The model is implemented in SPICE circuit simulators using Verilog-A based code.